APRIL 1976 \$1.50 (12 bits)

0

PP

D

ŏ

0

### the small systems journal

00

63

### WHY SETTLE FOR LESS-THAN A COMPLETE 6800 SYSTEM

### MEMORY-

All static memory with selected 2102 IC's allows processor to run at its maximum speed at all times. No refresh system is needed and no time is lost in memory refresh cycles. Each board holds 4,096 words of this proven reliable and trouble free memory. Cost only \$125.00 for each full 4K memory.

### INTERFACE-

Serial control interface connects to any RS-232, or 20 Ma. TTY control terminal. Connectors provided for expansion of up to eight interfaces. Unique programmable interface circuits allow you to match the interface to almost any possible combination of polarity and control signal arrangements. Baud rate selection can be made on each individual interface. All this at a sensible cost of only \$35.00 for either serial, or parallel type

### PROCESSOR-

"Motorola" M6800 processor with Mikbug<sup>®</sup> ROM operating system. Automatic reset and loading, plus full compatability with Motorola evaluation set software. Crystal controlled oscillator provides the clock signal for the processor and is divided down by the MC14411 to provide the various Baud rate outputs for the interface circuits. Full buffering on all data and address busses insures "glitch" free operation with full expansion of memory and interfaces.

### DOCUMENTATION-

Probably the most extensive and complete set of data available for any microprocessor system is supplied with our 6800 computer. This includes the Motorola programming manual, our own very complete assembly instructions, plus a notebook full of information that we have compiled on the system hardware and programming. This includes diagnostic programs, sample programs and even a Tic Tac Toe listing.

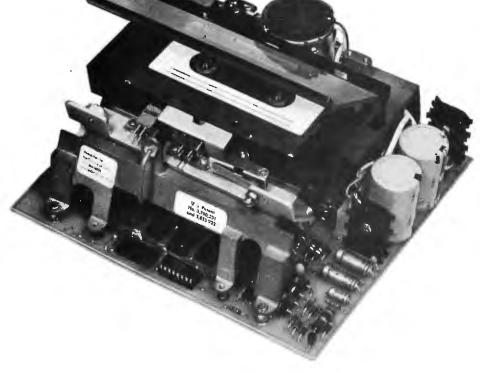

### POWER SUPPLY-

Heavy duty 10.0 Amp power supply capable of powering a fully expanded system of memory and interface boards. Note 25 Amp rectifier bridge and 91,000 mfd computer grade filter capacitor.

Mikbug<sup>®</sup> is a registered trademark of Motorola Inc.

Computer System

with serial interface and 2,048 words of memory.....\$395.00

| Enclosed is \$395 for   | r my SwTPC Computer Kit               | Send Data            |

|-------------------------|---------------------------------------|----------------------|

| or BAC                  |                                       |                      |

| or MC                   | Ex Da                                 | ate                  |

|                         |                                       |                      |

| NAME                    |                                       |                      |

| ADDRESS                 | · · · · · · · · · · · · · · · · · · · |                      |

| CITY                    | STATE                                 | ZIP                  |

| Southwest Technical Pro | ducts Corp., Box 32040, San           | Antonio, Texas 78284 |

TITLE: Microcomputer Dictionary & Guide AUTHOR: Charles J. Sippl and David Kidd

This new microcomputer dictionary fills the urgent need for all computer people, engineers, scientists, industrialists, communications people — as professionals, amateurs, teachers, or students — to become quickly acquainted with the terminology and nomenclature of a new revolution in computer control capabilities in areas that pervade most of man's daily activities.

Over 8000 definitions and explanations of terms and concepts (704 pages) relating to microprocessors, microcomputers and microcontrollers. There are also separate appendices on: programmable calculators; math and statistics definitions, flowchart symbols and techniques; binary number systems and switching theory; symbol charts and tables; summaries of BASIC FORTRAN and APL. In addition there is a comprehensive electronics/computer abbreviations and acronyms section.

(Also available from technical book stores and selected electronic distributors.)

### **MATRIX PUBLISHERS, INC.**

#### Dept. BM, 207 Kenyon Road, Champaign, IL 61820

Please send me the new MICROCOMPUTER DICTIONARY under your 15 day no risk trial guarantee. If payment accompanies order we pay all shipping and handling charges. (III. customers add 5% sales tax)

Name.

Address

City\_

State \_\_\_\_\_

Curiosity, experimentation and imagination are great aids to the user of a computer system. Charles A Crayne describes two instruction set variations he found while **Pro**gramming the Implementation of an 8008 processor as a SCELBI 8H minicomputer.

Can a computer predict your state of mind? A better question would be: Is there a theory which can be computationally verified to predict your state of mind? **Biorhythm for Computers** is an article by Joy and Richard Fox on the use of a BASIC calculation to provide predictions based upon the pseudo science of a simple biorhythm hypothesis.

A key element of computing is the expression of ideas in the form of programs and algorithms. It takes the **Magic of Languages** to make such expressions in a form the computer can understand. Turn to Theodor Nelson's article for an introduction to some basic concepts of computer languages.

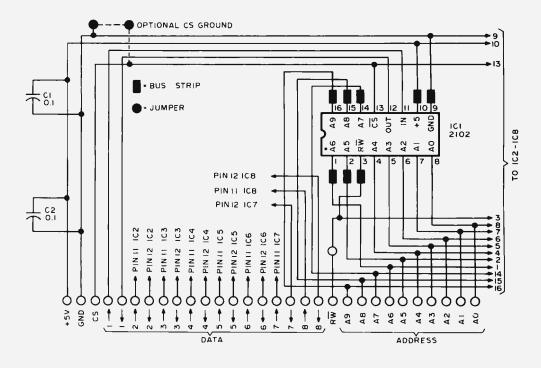

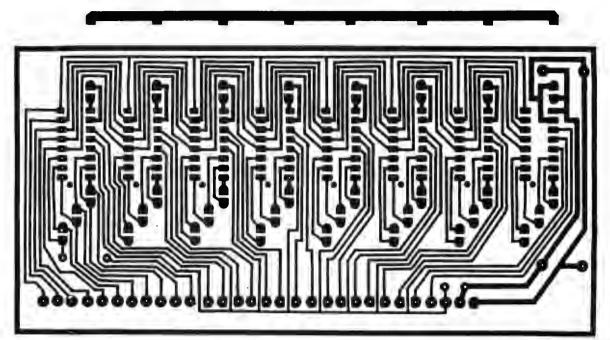

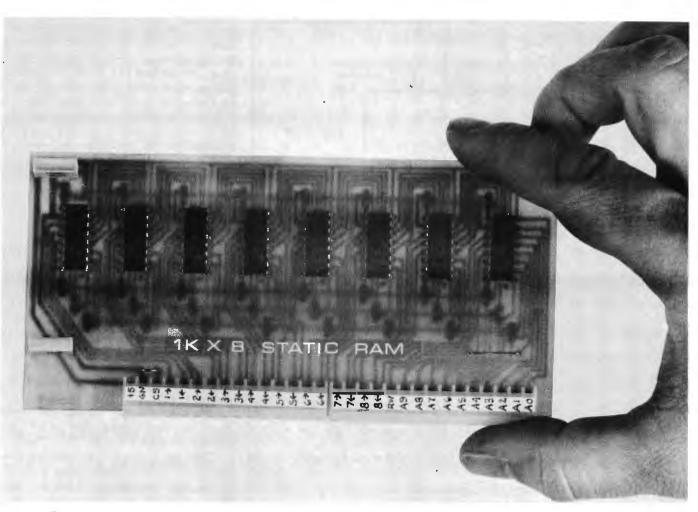

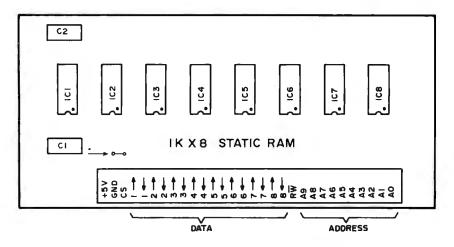

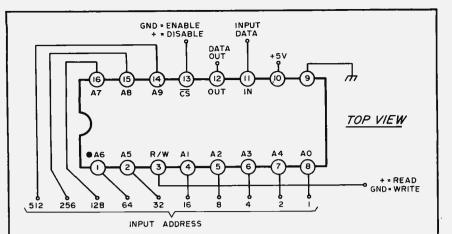

Ho hum, another memory article? Not quite. When Don Lancaster adds a twist of ingenuity, you find out How to Build a Memory With One Layer Printed Circuits, saving the trouble of using many wire jumpers or figuring out how to make double layer boards in the kitchen PC laboratory.

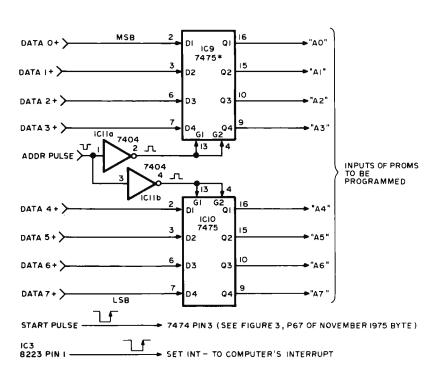

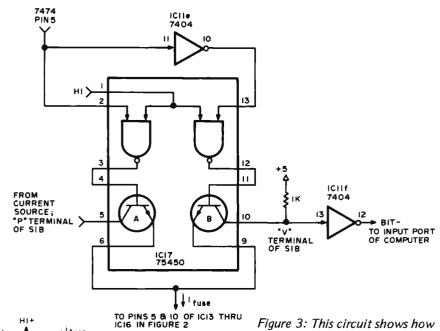

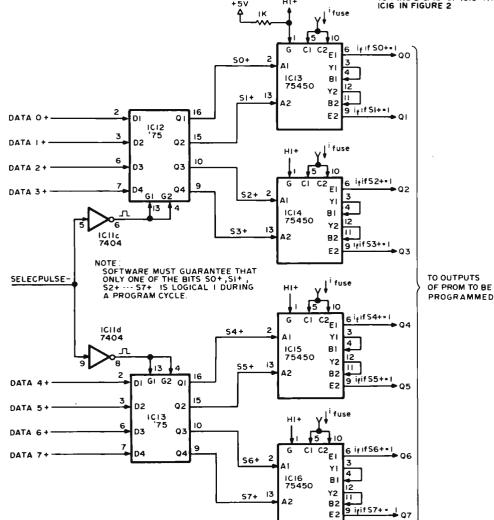

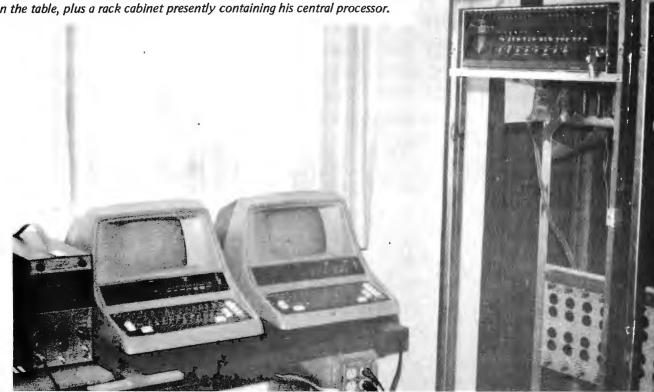

Aargh! (or, How to Automate PROM Burning Without EML) was Peter Helmers' reaction to a suggestion

# **In This BUTE**

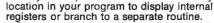

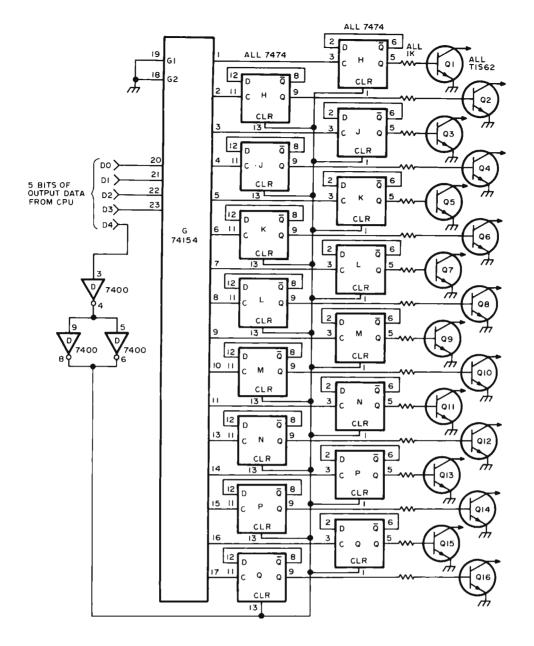

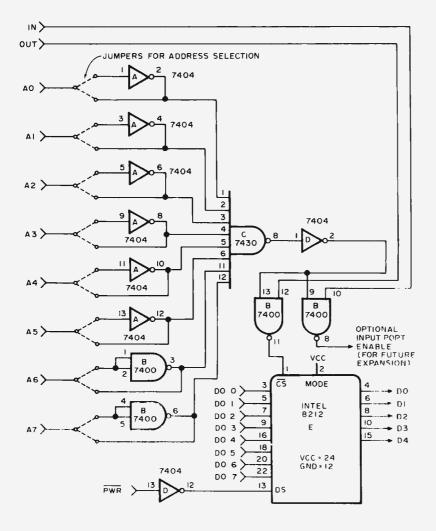

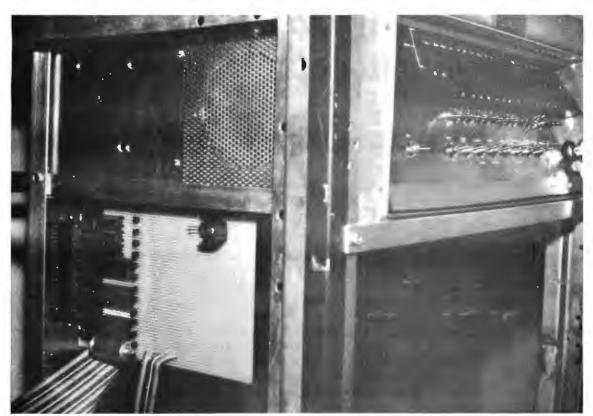

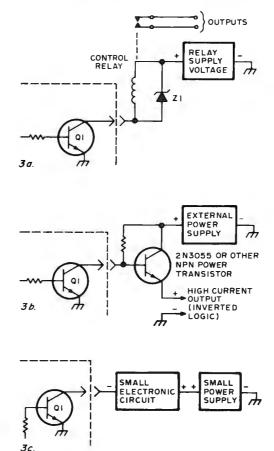

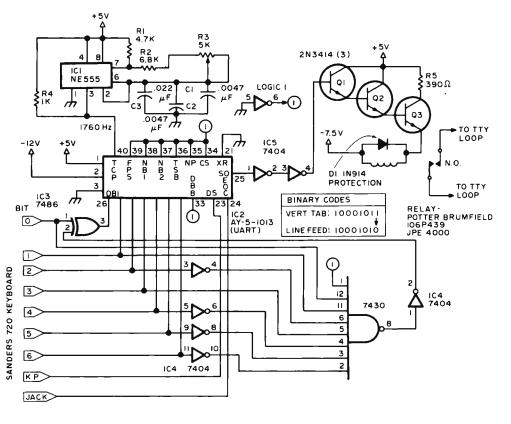

that relays be used to control a circuit. Study his figures for technical information and learn about the exciting new field of EML[sic] logic in the accompanying text.

It could not take long to find another contender in the marketplace for compact computer systems. In this issue, J Bradley Flippin discusses The SR-52: Another "World's Smallest Computer System."

Input is often done with a switch contact when simple on off states of electromechanical systems are considered. But suppose you want to program stage lighting or drive a keyboard machine with solenoids. Then you'll need information on Controlling External Devices with Hobbyist Computers. Robert J Bosen presents some ideas on the subject.

Computers require a large dose of that arcane art, interfacing. Jay A Cotton shows one example of that art in his discussion of how to Interface an ASCII Keyboard to a 60 mA TTY Loop.

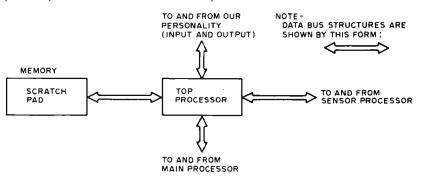

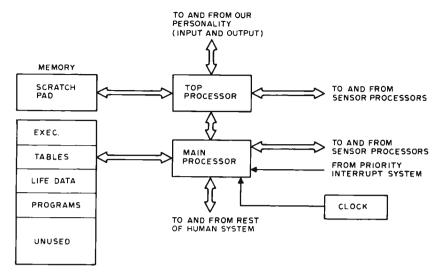

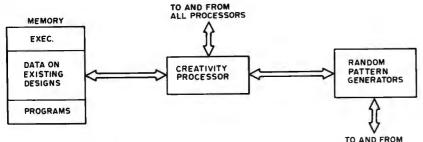

Introspection is a prime technique for analyzing the human consciousness. Many parallels can be drawn between the design of complicated computer networks and knowledge of human mental functions. While not purporting to be a complete or final model of human mental functions, Joe Murray's article on Frankenstein Emulation provides some good inputs on the ultimate hobby: modeling human behavior.

### A Note on the Current BYTE

Last month, the March issue of BYTE had a theme of magnetic recordings for digital data: four articles in that issue concerned various aspects of mass storage on the magnetic medium. This month, the theme is somewhat nebulous and is summed up by "April Fool!". The cover and several items in this issue are on a theme of far out applications and fun. I'll leave it to readers to figure out what items other than the cover fall into this category; however, all articles in this issue are instructive and informative, even those which are consistent with the theme. CH

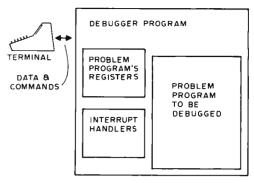

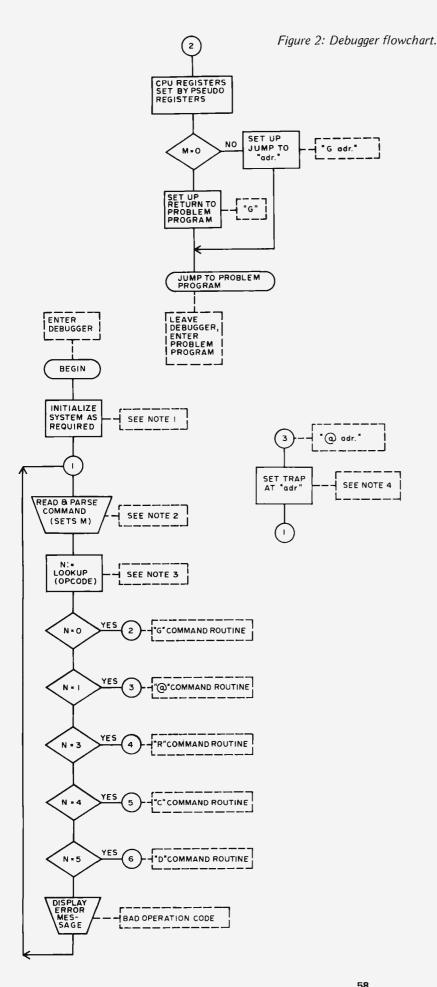

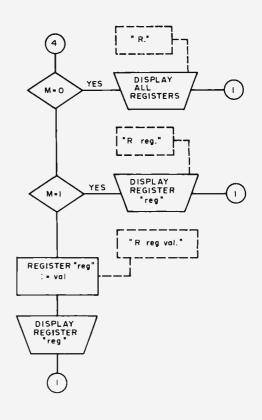

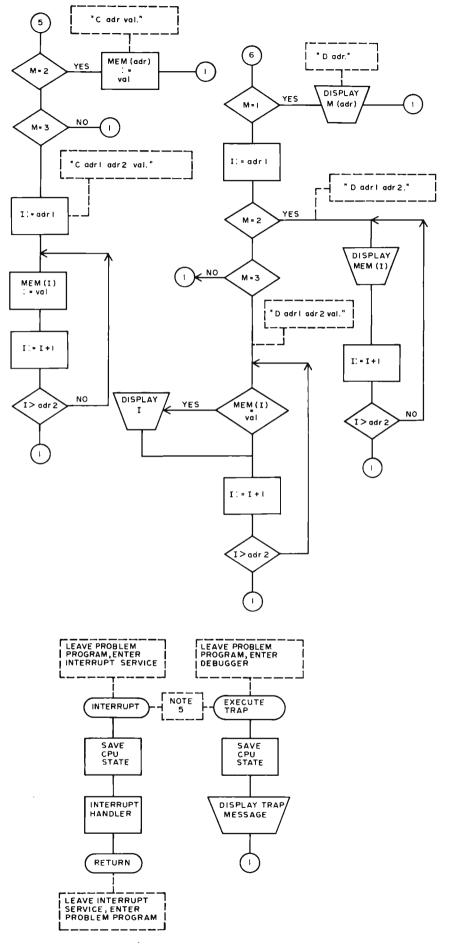

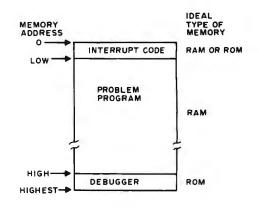

Minicomputers and microcomputers are really quite similar. The former are simply faster and more expensive than the current versions of the latter. Thus when you **Design an On Line Debugger** for a minicomputer, as Robert Wier and James Brown have done, the same general interactive design can be used as the control panel interface for any microcomputer as well. Add an on line debugger to your computer and you'll make it a much easier device to use.

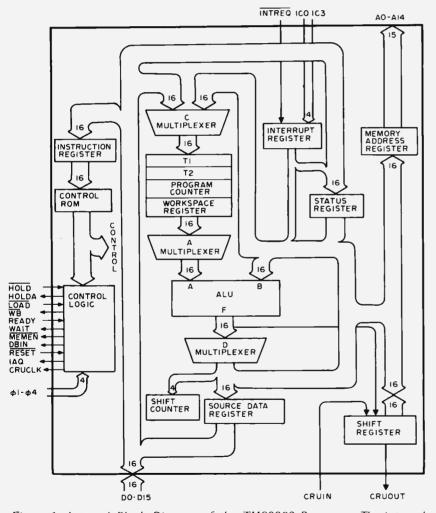

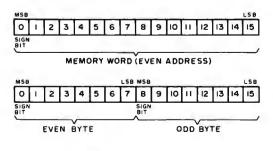

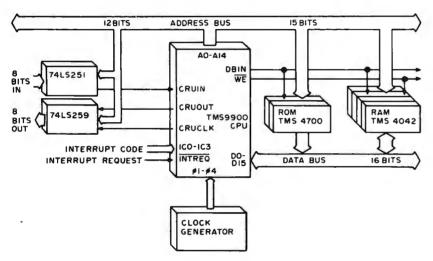

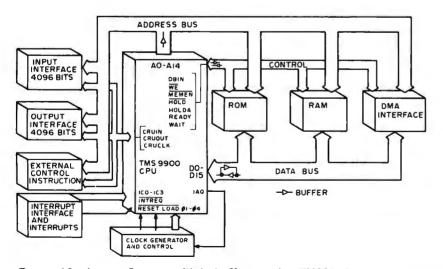

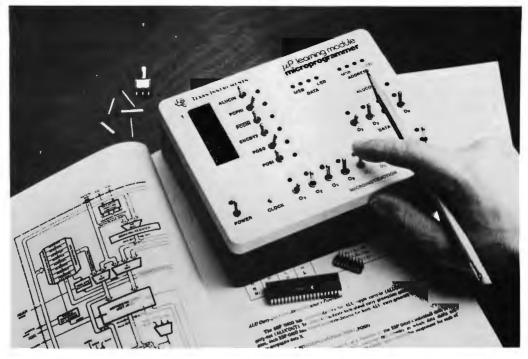

What's better than an 8 bit processor in a 40 pin package? Why, a 16 bit processor in a 64 pin package, of course. In his Microprocessor Update: Texas Instruments TMS9900, Robert Baker provides readers with an overview of this exciting new computer which is sure to find its way into personal computing systems over the next year or so.

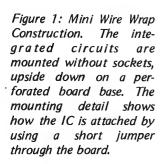

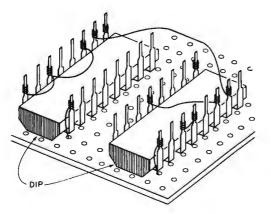

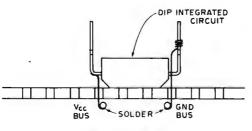

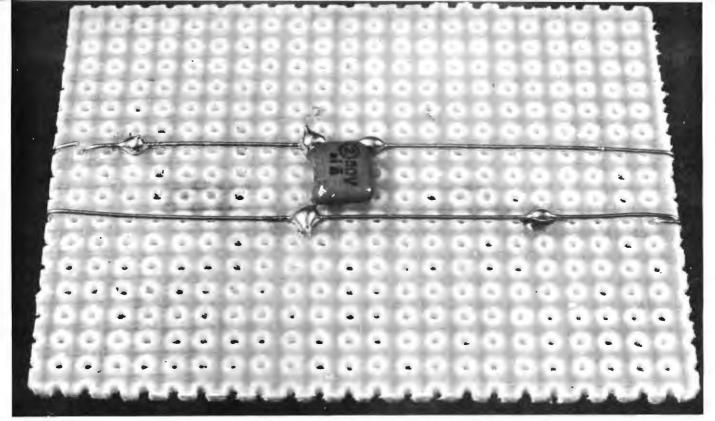

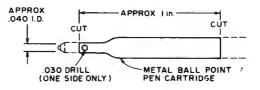

Ingenuity is an old American tradition. Roger W Thompson makes his contribution to that tradition in his description of how to Save Money Using Mini Wire Wrap, a socketless penny pinching way of wiring integrated circuit projects.

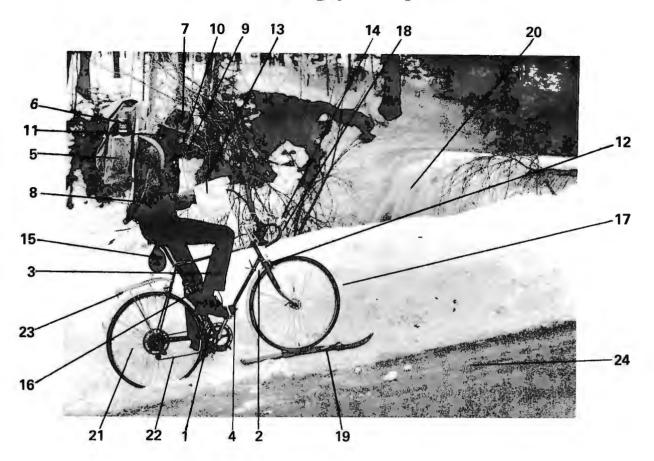

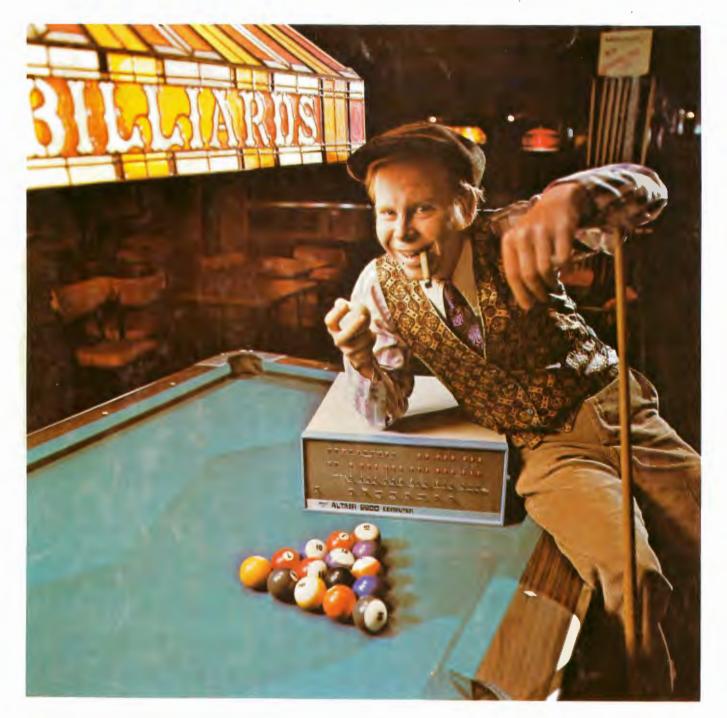

On the cover, at the suggestion of Tully Peschke, Robert Tinney created a fantasy on a theme of BYTE. First aid has already been applied and it is expected that the banner will be fixed in time for the May issue.

### In the Queue

BUTE #8

PUBLISHERS Virginia Peschke Manfred Peschke EDITOR Carl T Helmers, Jr GENERAL MANAGER Manfred Peschke

Judith Havey

Cheryl Hurd Carol Nyland Deena Zealy ADVERTISING Elizabeth Alpaugh Virginia Pesch ke TYPOGRAPHY

Elizabeth Alpaugh CIRCULATION Deborah R Luhrs

Goodway Graphics Mary Lavoie

Taimi Woodward PHOTOGRAPHY

**PRODUCTION MANAGER**

**PRODUCTION ASSISTANT**

PUBLISHERS ASSISTANTS

Custom Marketing Resources, Inc

**APRIL 1976**

staff

### Foreground

| 20 | BIORHYTHM FOR COMPUTERS<br>Application — Fox-Fox                              |

|----|-------------------------------------------------------------------------------|

| 28 | HOW TO BUILD A MEMORY WITH ONE LAYER PRINTED CIRCUITS<br>Hardware – Lancaster |

| 34 | AARGH! (or, HOW TO AUTOMATE PROM BURNING WITHOUT EML)<br>Hardware – P Helmers |

| 42 | CONTROLLING EXTERNAL DEVICES WITH HOBBYIST COMPUTERS<br>Hardware – Bosen      |

| 46 | INTERFACE AN ASCII KEYBOARD TO A 60 mA TTY LOOP<br>Hardware Cotton            |

| 56 | DESIGN AN ON LINE DEBUGGER<br>Software – Wier-Brown                           |

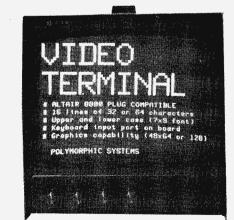

| 79 | IO STROBES FOR THE ALTAIR 8800<br>Hardware – Schulein                         |

| 80 | SAVE MONEY USING MINI WIRE WRAP<br>Hardware – Thompson                        |

### Background

| 16<br>24 | PROGRAMMING THE IMPLEMENTATION<br>Software – Crayne<br>THE MAGIC OF COMPUTER LANGUAGES | Ed Crabtree<br>Custom Marketing Resources, In<br>ART<br>Bill Morelio |  |  |  |

|----------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

|          | Software – Nelson                                                                      | PRINTING                                                             |  |  |  |

| 36       | THE SR-52: ANOTHER WORLD'S SMALLEST                                                    | Custom Marketing Resources, Inc                                      |  |  |  |

|          | Systems – Flippin                                                                      | The George Banta Company                                             |  |  |  |

| 50       | FRANKENSTEIN EMULATION                                                                 | ASSOCIATES                                                           |  |  |  |

| 64       | Speculations – Murray<br>MICROPROCESSOR UPDATE: TEXAS INSTRUMENTS TMS9900              | Dan Fylstra<br>Don Lancaster                                         |  |  |  |

| 04       | Hardware – Baker                                                                       | Harold A Mauch<br>Chris Ryland                                       |  |  |  |

### Nucleus

| In This BYTE                                  |

|-----------------------------------------------|

| Customization—The Expression of Individuality |

| Letters                                       |

| Space Ace Revisited                           |

| What's New                                    |

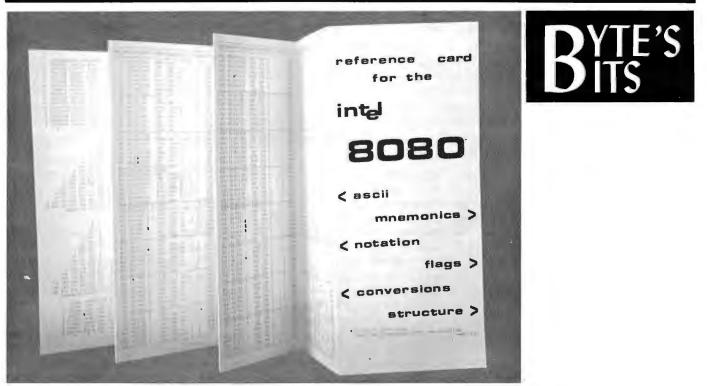

| BYTE's Bits                                   |

| Technology Update                             |

| BYTE's Bugs                                   |

| Classified Ads                                |

| Book Review                                   |

| Clubs, Newsletters                            |

| BOMB                                          |

| Reader's Service                              |

|                                               |

BYTE magazine is published monthly by BYTE Publications, Inc., 70 Main St, Peterborough, New Hampshire 03458. Subscription rates are \$12 for one year worldwide Two years, \$22. Three years. \$30. Second class postage application pending at Peterborough New Hampshire 03458 and at additional mailing offices. Phone 603-924-7217. Entire contents copyright 1976 BYTE Publications, Inc., Peterborough NH 03458. Acd Peterborough NH 03458.

### Customization --The Expression of Individuality

**Editorial by Carl Helmers**

Each person who gets involved in this activity of acquiring and using a personal computer system will sooner or later appreciate the results of customization. Each computer system comes out differently according to the tastes and creativity of its owner (to say nothing of his or her pocketbook). The number "n" of choices available in creating a personal system is large, and is getting larger every day.

### Individuality of Systems

Each personal computing system is an individual creation, despite the mass production genesis of all the parts and pieces. To understand this at a global level, simply consider the options available in the choice of standard microprocessor designs which make up the starting point for any system.

At the present time, there are kits on the market for half a dozen or so different microcomputer designs. The first expression of individuality you have to make is in your choice of the microprocessor design for your system. Choosing one such processor puts you into a group of people employing the same instruction set, a group which can share software experiences directly. These users are distinguished from the logical grouping of users associated with the other microprocessor architectures. (Note that the "user groups" for personal computing are logically a result of CPU choice since all users of the same chip design share common problems independent of the means of wiring up and packaging the computer.)

Having limited yourself to one particular microprocessor, the next level of exercising individuality in creating a system is your choice of a means to package and implement a processor using that CPU. Here again, the options are several. Some individuals "home brew" the packaging and system design with wire wrap or other interconnection techniques. Others elect to purchase a preengineered kit of parts from one of BYTE's advertisers. Whatever the choice of a basic system assembly with the processor, there are numerous system design options available to you. How much memory? What type of interactive display terminal? Will the system use audio tape or will it have a floppy disk as mass store? Does the supplier have a BASIC package? Does the supplier make an assembler, monitor and text editor available? Assuming a particular set of answers to these questions, you will end up with a fairly unique system, but one possibly identical at the start to the systems of several other individuals who use the same kit maker. What is the final step in customization?

### Modularity and Software

The customization of a system is ultimately achieved through the variations in the optional hardware modules attached to it, and through the personal library of software built up by the system's owner and user.

The customization of hardware starts in the choice of options available either from the manufacturer of the kit or from independent suppliers. There is presently only one family of compatible peripherals, those employing the MITS Altair backplane interconnection conventions. (For the present time, in order to have the widest choice of prepackaged component kits an Altair compatible bus is virtually a necessity.) If you purchase an Altair incompatible system. it will prove helpful to home brew an Altair compatible bus extension for interfacing such peripherals; if you engineer a home brew system, such an extension is also useful. (That is one project in my queue for my own home brew 6800 system.)

Once you have a basic system up and running, the customization of hardware continues in the choice of specific peripherals for applications, and in the choice of add on memory and hardware to augment the system as you continue to use it. Custom peripherals are required wherever a process control or sensing application is involved. If the computer is to control a model railroad, for instance, you'll have to custom design

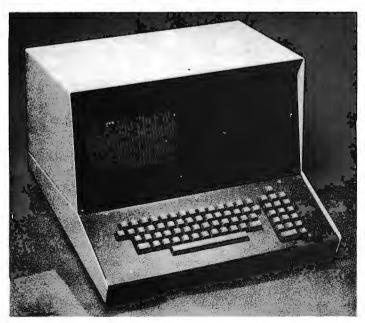

### Sphere Offers You A Real Computer!

### A REAL COMPUTER IS:

- 1. A SYSTEM: One that begins at the beginning with an attractive chassis to put everything in and consists of:

- A. CPU-To give the greatest computing power for the lowest cost ever. Motorola 6800 Microprocessor. The most advanced microprocessor available today.

- 1K PROM...The Computer Operating Program turns on instantly.

- 4K RAM...For storage and operating capacity for many programs.

- REAL TIME CLOCK...To program and monitor events outside and inside the computer.

- B. CRT-To display in human language on video everything going on inside the computer. (512 characters total in 16 lines by 32 characters.)

- C. KEYBOARD-So you can talk to your Computer as fast as you can type. (72 keys of alpha-numeric style typewriter keyboard.)

- AND A REAL COMPUTER ALLOWS YOU TO: Record and reload programs and data with inexpensive audio cassette recorder.

- D. SIM BOARD-So you can interface to teletype, audio cassette recorders and phone. (RS232c, TTL, TTY at 60ma and 20ma (Teletype), Modem, and 2 cassette recorders.

- 3. A REAL COMPUTER ALLOWS YOU TO: Add more memory so you can do more processing and have more storage space.

- E. 16K MEM BOARD-About 20 pages of close typewritten material (more memory up to 64K is available if needed.)

- 4. A REAL COMPUTER ENDS UP BY ALLOWING YOU TO: Remember huge quantities of information, and then print it out on paper when you need reports, records, checks, P.O.s, Invoices, etc., etc., etc.

- F. PIM BOARD-To interface the computer with the line printer and floppy disk storage.

- G. FLOPPY DISK-To remember ½ million characters (about 150 pages of typed material) on line with the computer.

- H. LINE PRINTER—To print 65 lines per minute on  $8\frac{1}{2}$ " wide paper up to 4 ledgible copies.

### THAT'S A COMPUTER!!!!

DELIVERY: 60-90 DAYS

### Please Contact One Of Our Distributors-

Computer Way-Huntington Beach, California Bargain Electronics-LaMeda, California Comput-O-Mat Systems-Rye, New York The Computer Workshop, Inc.-Montgomery County, Maryland Computer Mart Corporated-Boston, Massachusetts

The Computer Mart of New York-New York City, New York

Comunicacions S.A.—San Jose, Costa Rica Computer Country—Denver, Colorado

791 South 500 West Bountiful, Utah 84010 (801) 292-8466

### Letters

#### STAR TREK AND SPACE WAR FORUM

A number of readers have expressed interest in the use of personal computing equipment for STAR TREK and other space war games. Here is a collection of letters on the subjects. Continuation of the discussion and accounts of personal activities in this area are encouraged.

Members of the staff have been known to arrive at work two hours early in order to get their morning "fix."

#### OREGON STATE FORTRAN STAR TREK

In reply to the letters by Richard Wexler and Stewart Shelton regarding Star Trek and Spacewar, a version of Star Trek written in FORTRAN IV is currently being run on the CDC Cyber, under KRONOS 2.1, at the Oregon State University Computer Center, Corvallis OR 97331. The Spacewar to which Mr Shelton refers is, I believe, that which was publicized during the "National Spacewar Competition." My source of info on this was the DEC EduGram. I don't have access to this any more, but I believe it was in a late 1971 or a 1972 issue that the game was first described. DEC (Maynard MA) may be able to tell you more about this particular version. I am familiar with at least three other Spacewar games and would like to hear from other Spacewar freaks about different versions they might know of.

I've thoroughly enjoyed every issue of BYTE and can hardly wait for each new one. The only thing that bothers me is the lack of articles on programming theory. Will there be any sort of series covering such things as searching and sorting, parsing, tree structures, etc.?

> Chip Weems 728 Mildred Ln SE Salem OR 97302

### LARGE SCALE STAR TREK

... There has been considerable discussion of Star Trek (Spacewar) in the January issue. I'd like to pass on some information regarding the version of Star Trek we have currently running on a Data General Eclipse computer at work.

The genesis of the FORTRAN IV Star Trek program we have is unknown. We got it from a friend who got it from a friend who .... As far as I could tell, the code was Xerox FORTRAN although I physically got it on mag tape from a Varian 620i. The source code of the version we received was 1800 statements. Some effort was required for program transition to DG FORTRAN. We also spent considerable time debugging and cleaning up the code.

Our full program requires 25 K (16 bit words) of core for execution. We have 48 K of memory and operate background and foreground. Since the operating system (RDOS) takes about 16 K, any applications program over 16 K either steals the machine or severely limits the ability of the machine to support two users. (Particularly at lunch time when we make the machine available to computer games players.) Therefore, we broke the program into overlays to obtain a load module of 16 K. This works fine, but the disk sure rattles when torpedoes start flying. However, two players may play individual games at the same time. A further refinement was to compile the DG's FORTRAN 5 which significantly speeds execution and results in some saving of core (14 K).

This version of Star Trek is guite complex, although versions for large machines are even more complex. The game randomly determines the number of Romulans and Klingons in the Unholy Alliance and generates a reasonable number of Stardates in which to complete the mission. Automatic scoring of player proficiency is built in, along with appropriate insulting messages for those unfortunates who hit a star or meet their demise through other more sophisticated means. This game is not for the occasional player as a certain amount of skill is needed for full enjoyment. The program operates in simulated real time so the player with slow reactions is penalized.

Star Trek is an extremely addictive computer game. Members of the staff have been known to arrive at work two hours early in order to get their morning "fix." While most people quickly learn how to beat the general simple computer game and become bored with that game, very few can beat Star Trek with any regularity. No players have been

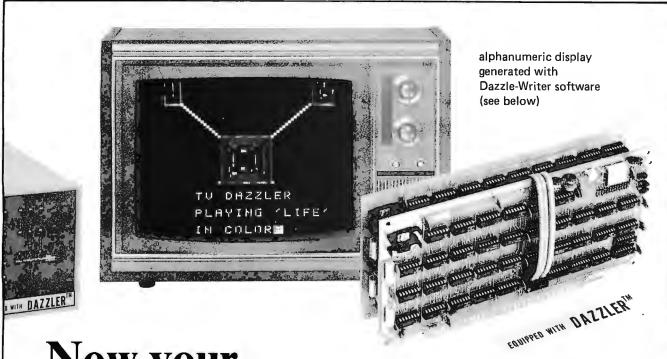

### Now your color TV can be your computer display terminal

#### New capabilities, too

Cromemco's new computer/tv interface circuit lets you have a full-color computer display terminal for little more than a black-and-white terminal.

The Cromemco interface also lets you do vastly more with your color terminal than you can do with ordinary black-and-whites. We call our interface the TV Dazzler<sup>®</sup>. It

directly into your Altair 8800 or IMSAI 8080 computer.

#### Alphanumerics plus action, and graphics

The Dazzler<sup>®</sup> maps your computer memory content onto your color tv screen in full color.

That doesn't mean just that you see alphanumerics in color. You can display *any* information in memory. And do so in color.

#### LIFE in color

You can display computer games or animated shows (rocket ships). What's more, you can display business or technical graphics — multi-colored charts, graphs, histograms, educational material — all from computer memory. Even light shows. Not even the biggest computer manufacturers offer all this in color.

### Needs only 2K memory

Technically, the Dazzler<sup>®</sup> scans your computer memory using direct-memory access (DMA). It formats each memory bit into a point on the tv screen to give a 128 x 128-element picture. Only a 2K-byte computer memory is required (only 512 bytes for a 32 x 32 picture). The quality of the pictures is evident in the photos.

The Dazzler<sup>®</sup> output is a video signal that goes directly to the tv video amp or to the antenna terminal through an inexpensive commercially-available device.

#### Inexpensive - and so much better

You can see from the list below that the Dazzler<sup>®</sup> is little if any more in price than an ordinary b/w interface or tv typewriter, But it does so much more.

#### Order now

By mail or at your computer store

If you're into computers (or want to be), if you want to invent these beautiful displays or games, or to plot colorful material inexpensively at home or in business, the Dazzler<sup>®</sup> is for you.

Not only is it reasonable, but it's sold at computer stores from coast to coast.

Or order directly by mail on your bank card.

| TV DAZZLER® (complete kit) . |   | \$215 |

|------------------------------|---|-------|

| TV DAZZLER® (fully assembled |   |       |

| and tested)                  | • | \$350 |

|                              |   |       |

| SOFTWARE                     |   |       |

| 001110/01                   |     |    |    |        |  |

|-----------------------------|-----|----|----|--------|--|

| (punched paper tape with do | cui | ne | nt | ation) |  |

| LIFE in full color          |     |    |    | . \$15 |  |

| KALEIDOSCOPE in full color  |     |    |    | . \$15 |  |

| DAZZLE-WRITER (for alpha-   |     |    |    |        |  |

| numeric displays in color)  |     |    |    | . \$15 |  |

Shipped prepaid if fully paid with order. California users add 6% sales tax.

Mastercharge and BankAmericard accepted with signed order.

Delivery: from stock for immediate shipment.

It's like being pioneers spirits are high and there is a wilderness to contend with. known to become bored over an extended period of time.

Since such an extensive game as we have available is not useful to the average hobbyist on his micro, it seems reasonable that many will turn to one of the BASIC versions of Space War such as you have referenced as being available in the DEC book of 101 BASIC Games. Your January book review failed to mention that the reproduction quality of programs in that book varies for each of the programs. Unfortunately, the reproduction of Space War in that book is very hard, if not impossible to read, because the master was obtained from a Teletype that was not properly aligned. The bottoms of the characters are cut off in the copy of the book that I bought. However, most of the programs in that book are reproduced quite well and I would add my general endorsement to your book review.

I enjoy BYTE and would add my vote to others you have received regarding the happy combination of ham radio and computers as the source of future articles.

> Dave Vandaveer Santa Ana CA

### SOME SPACE WAR BACKGROUND

Regarding the enquiry concerning Space War (page 86, January BYTE) I can agree that it is a stimulating, dynamic (and therefore very time-consuming) game. Its origins are shrouded in mystery, but it is part of a standard demonstration packet released by DEC for their machines with graphics capability, such as the PDP-12 or the GT40 system. The essence of the game is the control of two rockets (displayed on a CRT) which have missile-firing systems; the object is to blast your dreaded enemy from the spaceways. Most versions use four bitcontrolled parameters for each ship: rotate up, rotate down, fire thruster and fire missiles. More elaborate versions include meteorite obstacles, a central sun which modifies trajectories due to its gravitational pull and "space warp," the ability to disappear when threatened with incipient destruction (but not know when or where you will reappear).

The most primitive version of the game will run in a PDP-8 with 4 K. There must be some provision for graphics display, either a point-plotter or DA converters and a CRT. Control can be via console switches, and timing is aided by a real time clock, although this latter requirement is not necessary. The main problem with running the game on a micro is word size. Velocity and position of the rockets is calculated iteratively, and small roundoff errors yield large net changes as the game goes on. For this reason, all parameters are calculated double precision (24 bit) on the PDP-8, which is triple precision on most micros. The increased overhead as a result of this requirement may spoil the timing and slow the game down, although the PDP-8 executes a complete update loop in somewhat less than 10 ms, and this can be slowed to about 30 ms before the onset of noticable flicker. The display may pose a problem as well, since 10 bit resolution on a CRT is acceptable, but 8 bit may be pushing things a bit.

> A B Bonds, PhD Berkeley CA

### NAVIGATING AN OCEAN OF INFORMATION

First, let me say that I'm enjoying BYTE very much and look forward to each new issue.

The microcomputer system I've built uses an 8008 but will eventually expand to symbiosis with an 8080 CPU. I want to express my happiness that you are not abandoning those of us hobbyists who have 8008 based machines. I know all too well the limitations of the 8008, but I think it is still a superb way to start out. The 8008 instruction set almost immediately inspires affection with its non-threatening three letter mnemonics and their nice correlation to octal number representation.

I think most of us know that we're into a unique thing with this burgeoning new baby of a hobby. It's like being pioneers - spirits are high and there is a wilderness to contend with. Big time centralized computers were not a panacea for the world's ills. The new wilderness we face is information glut and it threatens to swamp us more essentially at the individual level than at the institutional level. Microcomputers are a new tool that promise deliverance. They can be a seemingly playful tool, but they possess the power to navigate that ocean of information which modern man must sail upon. Well, I just wanted to philosophize a little and say that I think this new hobby (and BYTE) will be an aid to us all.

> Adam Trent Ascension Island Patrick AFB FL

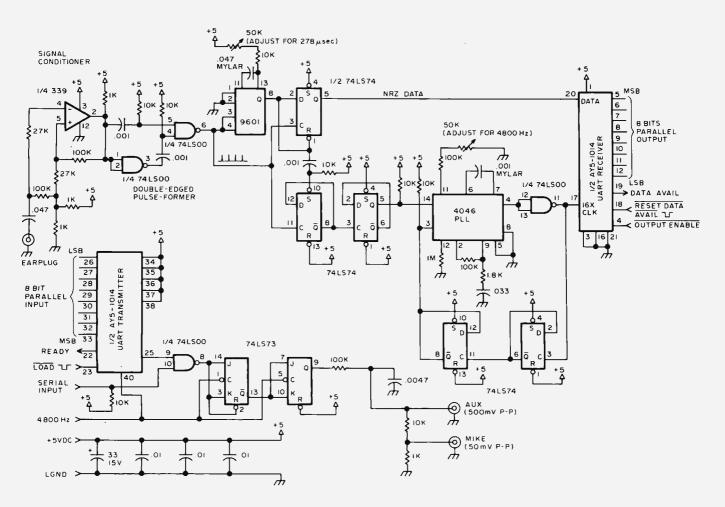

### AN IMPROVED CASSETTE INTERFACE CIRCUIT

As might be expected, we have made some changes and improvements to our cassette interface circuit which will be of

# The One and Only

# Altair 4K Static.

Altair 4K Static from MITS is unquestionably the finest 4K static memory available anywhere. It is also the fastest.

Altair 4K Static uses Intel 2102 A-4 memory chips which have a worst case access of 450 nanoseconds at 70 °C. At normal system temperatures the access times are typically less than 300 nanoseconds.

Altair 4K Static is fully isolated from the system bus by Schmitt<sup>™</sup> Triggers. Thus, the excessive capacitive loading caused by other 4K static memories is eliminated. Use of these triggers on all Altair 4K static inputs greatly reduces noise. Internal data collection nodes also use Schmitt Triggers, which prevents internal data bus noise from being transmitted to the system data bus.

Altair 4K Static is the only 4K static supported by MITS. Owners of Altair 4K Static are eligible to qualify for discounts on AltairBASIC and other MITS products.

Altair 4K Static is the only 4K static that comes with all the required Altair hardware including edge connectors and card guides.

Altair 4K Static is the answer for Altair owners who need static memory for special applications such as the TV Dazzler from Cromemco.

### PRICES:

| Altair 4K Static Kit.                |   | \$159 |

|--------------------------------------|---|-------|

| Altair 4K Static Kit with 2K Memory. |   | \$134 |

| Chip set to convert 2K to 4K         | • | \$45  |

**SPECIAL**—Altair Documentation Notebook. Contains catalog, price sheet, Computer Notes newspaper, Software Information Package, technical data on Altair hardware, list of authorized Altair dealers, list of computer clubs, survey of home computing market, and much more. All in top quality three ring binder. Only \$5 plus \$1 for postage and handling. Offer expires April 30, 1976.

#### MAIL THIS COUPON TODAY

|                                  |               | ·          | a da la  | 10      | 43           |          |            |                     | 1230  |        |        | , venter |

|----------------------------------|---------------|------------|----------|---------|--------------|----------|------------|---------------------|-------|--------|--------|----------|

| BankAmerica<br>Altair 4K Stat    | rd #          |            |          |         | _or /        | Maste    | r Cha      | rge #               |       |        |        |          |

| Include \$3 fo<br>Please send in | r postag      | e and      | l han    | dling   |              | NA       | ahool      | E.,                 | lose  |        | s alu  |          |

| postage and I<br>Please send f   | bandling      | <b>.</b> S | 19       |         |              |          | - <u>1</u> | <b>u</b> m<br>://// | .iose | u 13 9 | o pias | · • • •  |

| NAME                             |               |            |          | - 2     |              |          |            |                     |       |        |        |          |

| ADDRESS                          | · · · · · · · |            | - 13 A T | 1975. · | 1 1991<br>19 | <u> </u> | 97 MSS     | - diare             |       |        |        |          |

| CITY                             | in the second | Sec. 1     | 4        | 8. Qu   | da           | ST       | TE .       | 710                 | 184   |        | 1.18   | 1.38     |

Prices, delivery and specifications subject to change.

2450 Alamo SE/Albuquerque, NM 87106/505-262-1951

interest to your readers. These improvements were still being worked out when I submitted the article ("Digital Data on Cassette Recorders," page 40, March 1976 BYTE), hence they were not included.

We were quite disappointed in the performance of the 4047 as a retriggerable one shot, therefore we went back to the 9601 or 74122 we had used in earlier designs. We have also eliminated the need for  $\pm$  12 volt power supplies by changing the design of the signal conditioner circuit and by using the AY5-1014 UART. The entire circuit now operates from a single 5 volt supply.

We discovered the circuit described in the article was sensitive to the polarity of the received signal from tape. To eliminate this sensitivity we went back to a double edged pulse former. This required the one shot period to be reduced to 278 microseconds and the elimination of one of the flip flops in the Phase Locked Loop feedback divider string. Adjustment is the same as before.

Some hobbyists who have seen the circuit have wondered why we used the 339 Quad Comparator for the signal conditioner since only one section was used. The Pronetics circuit card uses one of the remaining sections as a level sensor to inform the user of proper playback level. Another section is used to indicate when data is being received from tape and the remaining section is used to drive a relay which remotely controls the cassette tape unit. If these functions are not necessary a 311 comparator can be substituted for the 339.

We designed out most of the CMOS integrated circuits because of handling problems in low humidity (static discharge destruction of gates). The 4046 PLL was retained to permit operation with a single 5 volt power supply.

Enclosed is a drawing of the improved circuit. If your readers have any questions I will be happy to answer if they include a self addressed stamped envelope.

> Harold A Mauch 4021 Windsor Garland TX 75042

### RTTY AND MORSE

So far, I have found your magazine excellent in all respects. You appear to be on top of all the latest machines and devices on the market, and the articles are timely and continued on page 71

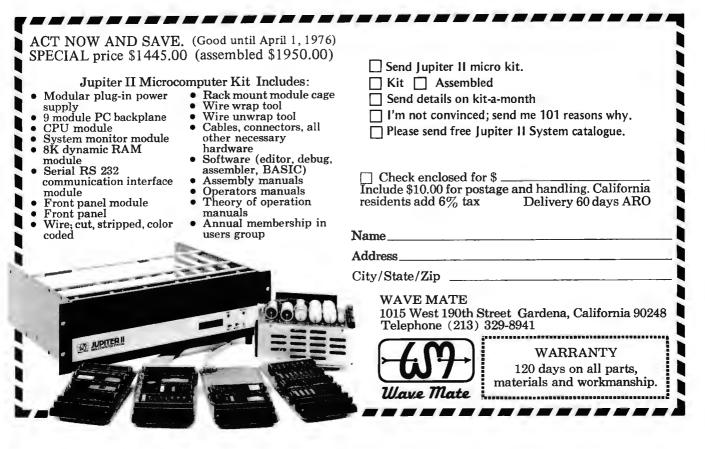

## You can buy this microcomputer for \$39.95, but...

We would be a bit surprised if you could do anything meaningful without additional hardware and software.

In fact every part including the powerful MC 6800 CPU and the 8K dynamic RAM is guaranteed for 120 days. It has the best ware around System Monitor and Debug

Wave Mate's Jupiter II<sup>™</sup> isn't the kind of microcomputer kit you only stare at... when you've completed your Jupiter II just plug in your terminal and you're ready to go. That's because it goes beyond the sum of its high quality parts. It's the ultimate micro kit experience. In performance, in documentation, in reliability. First, consider its superb features. It has small pluggable wire wrapped cards easily tailored to suit your modifications. Every IC is socketed and 100% burn-in tested. software around, System Monitor and Debug programs (ROM). Includes powerful text editor and Motorola compatible assembler. And BASIC at no extra cost. Because we've been making microcomputer systems for over 4 years, we can offer you the broadest line of interfaces including TV terminal and dual audio cassette. Impressive. And yet the

grandest feature is the experience of completing a kit that works. Guaranteed.

April Fool came a little early with Space Ace. We aced out on Bob Baker's puzzle in March BYTE, page 77, by omitting the word list. Here it is again, with the word list. Answers will appear in May BYTE.

| N | F        | S |        | в | R  | ļ     |   | Т |   | N |   | S  |   |   | Р |

|---|----------|---|--------|---|----|-------|---|---|---|---|---|----|---|---|---|

|   | R        |   | С      |   | R  | D     |   | M |   | N | S |    |   | Ν | R |

| т |          |   | T      | Р |    | <br>T | R |   | Т |   | R |    | Р |   |   |

| w | R        |   | ·<br>T | • | X  | T     |   | R | N |   | L | R  | - |   | G |

|   | D        |   | C      |   | D  | •     | С | N |   |   |   |    | N | S | R |

|   | L        | В |        |   | R  |       | v | S | G |   | В | w  | C |   |   |

|   | <b>L</b> | D |        |   |    |       |   | 3 |   |   |   | VV |   |   |   |

| С |          |   |        | D | N_ |       | P |   | N | Τ | R |    | H | С | M |

| Ν | Т        | Ν | М      | R | Т  |       | С |   |   |   |   | N  |   |   | Η |

|   | С        | Т |        | Ρ | С  |       |   | С | М | G | R | D  | Ν | R | Т |

| L |          |   | Т      |   | L  | S     | R |   |   |   | Y | N  | Т | Ρ |   |

|   | М        | G |        |   | S  |       | N | L | L | Т | Ν |    | R | Ρ | R |

| V | Р        |   | D      |   | D  | Р     | С | L |   |   | L | F  | Υ |   |   |

|   | L        | R | R      | L |    |       |   |   | S | L |   |    | R | R | G |

|   |          | Ρ |        | Т | Y  | Р     |   |   | Т |   | N |    | В | R |   |

| Q | Х        |   | S      | С |    | L     |   | R | L |   | Т |    | R |   | L |

|   | F        |   | N      | С | Т  |       |   | N | G |   | S | S  |   | Υ | L |

### Space Ace

By inserting the missing vowels (a, e, i, o, and u) in the appropriate blanks, all 50 words from the list will fit into the matrix. As you find each word and insert the correct vowels, circle the word in the matrix and cross the word off the list. Words may be forward, backwards, up, down, or diagonal,

location, but only one position is correct.

but always in a straight line, never skipping letters. However, some of the letters are used more than once. After circling all the words on the list, the seven remaining letters (including two blanks for vowels) in the matrix will spell the name of a high level computer programming language these words are related to. Be careful, though; some words may appear to fit in more than one place in the matrix. There is, however, only one correct position for each word, so that all the words from the list will be used.

| ARRAY                 | EXPRESSION              | LOGICAL   | *REAL      |

|-----------------------|-------------------------|-----------|------------|

| ASSIGN                | EXTERNAL                | LOOP      | RECORD     |

| BUG                   | FIELD                   | NAMELIST  | RETURN     |

| CALL                  | FIND                    | *NOT      | REWIND     |

| COMPLEX               | FUNCTION                | OCTAL     | SCALAR     |

| *DATA                 | *GOTO                   | OPERATOR  | SPACE      |

| *DECODE               | IMPLICIT                | OUTPUT    | STOP       |

| DIMENSION             | INTEGER                 | PAUSE     | SUBROUTINE |

| ENCODE                | *LABEL                  | PRECISION | *TAG       |

| *END                  | LIBRARY                 | PRINT     | TYPE       |

| ENTRY                 | LITERAL                 | PROGRAM   | *UNIT      |

| EQUIVALENCE           | LOGARITHM               | PUNCH     | VARIABLE   |

| * = words that appear | to fit in more than one | *READ     | WRITE      |

Robert Baker 34 White Pine Dr Littleton MA 01460 For a limited time only, you can own an Altair<sup>®</sup> 8800 Computer kit with 4,096 words of memory, new Altair multi-port interface, and revolutionary Altair BASIC language software, for just \$695. A savings of up to \$114!\*

**Computer.** The Altair 8800 is the best-selling general-purpose computer in the world today. It is a parallel 8-bit word/16-bit address computer with an instruction cycle time of 2 microseconds. It was designed for almost unlimited peripheral and memory expansion, using a bus system where all input/output connections merge into a common line. The Altair 8800 is capable of addressing up to 65,536 words (bytes) of memory. *Regularly priced at \$439 for a kit and \$621 assembled.*

**Memory.** The Altair 4K Memory Board provides 4,096 words of dynamic random-access-memory for the Altair 8800. Contains memory protect circuitry, and address selection circuitry for any one of 16 starting address locations in increments of 4K. Access time is 200-300 nanoseconds. The entire 4,096 words of memory on the board can be protected by switching to PROTECT. *Regularly priced at \$195 for kit and \$275 assembled.*

Interface. Your choice—either the new Altair 88-2510 serial interface or the new Altair 88-4P10 parallel interface. The serial interface can be ordered with either one or two ports and the parallel interface can be ordered with up to four ports. Add \$24 for an additional 88-2510 port kit. Add \$30 for each additional 88-4P10 port kit.

Each port of the new serial interface board is user-selectable for R5232, TTL, or 20 milliamp current loop (Teletype). The 88-2SIO with two ports can interface two serial I/O devices, each running at a different baud rate and each using a different electrical interconnect. For example, the 88-2SIO could be interfaced to an R5232 CRT terminal running at 9600 baud and a Teletype running at 110 baud. An on-board, crystal-controlled clock allows each port to be set for one of 12 baud rates. The 88-2SIO is regularly priced at \$115 kit and \$144 assembled.

Each port of the *new parallel interface board* provides 16 data lines and four controllable interrupt lines. Each of the data lines can be used as an input or output so that a single port can interface a terminal requiring 8 lines in and 8 lines out. All data lines are TTL compatible. The 88-4PIO regularly sells for \$86 kit and \$112 assembled.

**Software.** Altair 4K BASIC leaves approximately 725 bytes in a 4K Altair for programming which can be increased by deleting the math functions (SIN, SQR, RND). This powerful BASIC has

16 statements (IF . . . THEN, GOTO, GOSUB, RETURN, FOR, NEXT, READ, INPUT, END, DATA, LET, DIM, REM, RESTORE, PRINT, and STOP) in addition to 4 commands (LIST, RUN, CLEAR, NEW) and 6 functions (RND, SQR, SIN, ABS, INT, TAB, and SGN). Other features include: direct execution of any statement except INPUT: an "@" symbol that deletes a whole line and a " $\leftarrow$ " that deletes the last character; two-character error code and line number printed when error occurs; Control C which is used to interrupt a program; maximum line number of 65,529; and all results calculated to seven decimal digits of precision. Altair 4K BASIC is regularly priced at \$60 for purchasers of an Altair 8800, 4K of Altair memory, and an Altair I/O board. Please specify paper tape or cassette tape when ordering.

Savings depends upon which interface board you choose. An Altair 4K BASIC language system kit with an 88-2SIO interface regularly sells for \$809. With an 88-4PIO interface, this system sells for \$780.

NOTE: Offer expires on March 30, 1976.

MITS/6328 Linn N.E., Albuquerque, NM 87108 505/265-7553 or 262-1951

MAIL THIS COUPON TODAY!

| Enclosed is check for 5          |                                   |

|----------------------------------|-----------------------------------|

|                                  | 🖸 or Master Charge #              |

| 🗌 Altair BASIC System Special 🖾  | 1 4PIO interface 🔲 2510 interface |

| Cassette tape 🖾 or paper tape    |                                   |

| Extra SIO port E                 | (PIO ports                        |

| Add 58 for postage and handling. |                                   |

| D Please send free literature    |                                   |

| NAME                             |                                   |

| ADDRESS                          |                                   |

| CITY                             | STATE & ZIP                       |

NOTE: Personal checks take 2-3 weeks for clearance. For immediate processing send money order or use charge card. Delivery: 30 days. Prices, specifications and delivery subject to change.

### What's New?

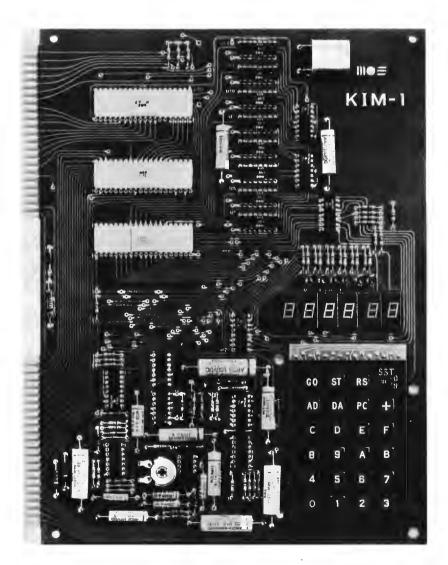

### What's New, KIM-o-sabee?

MOS Technology Inc has announced a new microcomputer system which is being marketed to individual hobbyists as well as to the standard industrial markets. This marks a "first" for the personal systems marketplace – a semiconductor manufacturer recognizing the potential of the hobbyist market and selling directly to it. The product is the KIM-1 Microcomputer System. At press time, early information describes KIM-1 as follows:

- 6502 processor (see "Son of Motorola" by Dan Fylstra in November 1975 BYTE, page 56).

- Completely assembled (not a kit).

- Supplied with the new KIM-1 manual and over 400 pages of MOS Technology's excellent 6500 series documentation. (The 6500 Family Programming Manual has some excellent tutorial information as well as specifics on the 6500 family computers.)

- Systems software contained in 2048

bytes of ROM in two 6530 ROM/ RAM/IO arrays.

- 1024 bytes of static user RAM.

- 23 key keyboard for programmed inputs and control of the monitor.

- 6 digit LED display for programmed outputs and monitor displays.

- General purpose serial interface with automatic line speed sensing and adaptation. Communications rates from 110 baud to 1200 baud are supported for devices like Teletypes and video display terminals.

- Audio cassette interface (FSK ratio recording).

- 15 bidirectional programmable IO pins to control experimental applications.

- 1 MHz system clock controlled by a crystal.

The board requires a power supply of +5 volts at 1.2 amperes for operation of the computer and LED displays. With this single power supply, you can unpack it from its carton and demonstrate programmable operation with the onboard keyboard and displays. Add a second 12V 0.1 ampere supply, and the audio cassette interface can be exercised with your inexpensive cassette recorder.

This product will prove attractive to readers who are not inclined to fondle hardware extensively, but want a programmable machine with the minimum amount of trouble.

### Glorobots

A robot was having conniptions at reading handwritten inscriptions, but acquired the knack by decoding a stack of typical doctor prescriptions.

### Evolution

A self-evolved robot named Babbitt, because of his dubious habit of unbridled mating and self-propagating, was housed in a hutch like a rabbit.

### Hear Ye Hear Ye

The sensory robots are near, but will not be ready this year, for each of them tries to eat with his eyes, and cocks his nose trying to hear.

> Gloria Maxson 13602 Cullen Whittier CA 90605

### • A COMPLETE MICROCOMPUTER

- ONLY \$245

- NOT A KIT! • FULLY ASSEMBLED

- FULLY TESTED

- FULLY WARRANTED

- **OPERATES WITH**

- KEYBOARD & DISPLAY

- AUDIO CASSETTE

- TTY

- KIM-1 INCLUDES

- HARDWARE

- **KIM-1 MODULE WITH** 6502 μP ARRAY 6530 ARRAY (2) **1 K BYTE RAM 15 I/O PINS**

- SOFTWARE MONITOR PROGRAMS (STORED IN 2048 ROM BYTES)

- FULL DOCUMENTATION **KIM-1 USER MANUAL** SYSTEM SCHEMATIC 6500 HARDWARE MANUAL 6500 PROGRAMMING MANUAL 6500 PROGRAMMER'S **REFERENCE CARD**

| USE THIS FORM TO                      | ORDER YOUR KIM-1 IODAY!                                                                                                                                              |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | Please ship me KIM-1 Systems at a cost of \$245.00 per system plus \$4.50 for shipping, handling and insurance (U.S. and Canada only) PA residents add 6% sales tax. |

|                                       | (International sales subject to U.S. Commodity Control Regulations,<br>Add \$20.00 per system for shipping and handling of international orders.)                    |

|                                       | My check or money order is enclosed for \$                                                                                                                           |

| CHNOLOGY, INC.<br>950 Rittenhouse Rd. | Name                                                                                                                                                                 |

| stown, PA 19401                       | City State Zip                                                                                                                                                       |

|                                       |                                                                                                                                                                      |

### Programming the Implementation

Look for logical gaps in the design of a specific system, then ask yourself: "What would happen if I did something that is technically undefined for my computer?"

Charles A Crayne 734 S Ardmore Av Los Angeles CA 90005

An exploration of the Scelbi 8H reveals two single byte instructions which are artifacts of the implementation: Load minus 1 immediate (L11) and read option switches (ROS). When Scelbi Computer Consulting Inc designed their 8H minicomputer system around the Intel 8008 CPU chip, they implemented two instructions beyond those available on the Intel chip. It seems that these two instructions are a byproduct of the 8H design, and of potential interest to the hobbyist.

The term "architecture" generally means the design of a system, or of a family of systems. The instruction set, maximum address, number of ports, etc., are architectural considerations affecting the design of a chip. The term "implementation" refers to the technical methods used to bring the defined capabilities into existence; this may be accomplished by backplane wiring, or ROM, number and speed of clocks, choice of power supplies, etc.

The distinction between architecture and implementation is clearer for a computer "family" than for a single device. In the IBM line, for example, all 370s share a single architecture. The difference between a model 115 and a model 168 is implementation. Note also that a designer is not required to implement the full capacity provided by the architecture. On the Scelbi 8H, the architecture provides for 16 K bytes of main storage, but the implementation allows for only 4 K bytes.

At first glance, the matter of the Scelbi 8H input ports is just another example of implementing less than the full architectural capacity. Eight input ports are allowed for in the instruction set, but only six are provided. A surprise is in store, however, for anyone who asks himself the question, "What would the computer do if I called for input from port 6 or port 7?" (The eight possible ports are numbered from 0 to 7.)

To answer this question, it is necessary to consider just why Scelbi decided to provide only six input ports. This can be resolved by a glance at the logic diagram for the Scelbi input board. The function of this board is to couple the 8008 data bus, at the appropriate times, to one of the input ports, the external memory data bus, or (in the case of a front panel interrupt) to the front panel data switches. This switching operation is implemented with type 74151 ICs, which are one of eight data selectors. That is, they will accept eight bits of input, and will output one of the eight, depending upon the three bit address (000 to 111) supplied at the time the enable line goes high.

The Scelbi designer needed a one of ten selector to accommodate the eight input ports, the memory bus, and the panel switches. But binary addressing just doesn't work that way. He could use a one of 16 selector and leave six inputs unused, or he could do as he actually did and use the 74151s by reducing the number of input ports implemented to six. This decision resulted in a lower cost system. Logic is provided to force the selector addresses to 110 for memory input operations, and to 111 during interrupt processing. But, again, probably for cost reasons no logic is provided to assure that the address specified in an input instruction is limited to the 000 to 101 range (IN0 to IN5).

Therefore, the IN6 instruction (input from port 6) causes the accumulator to be set from the memory bus, and the IN7 instruction causes the accumulator to be set from the front panel switches. Unlike the LAM instruction, however, IN6 does not cause the memory address to be developed. Therefore, the result of the instruction is to load the accumulator with the value -1 or 377 in octal. This is not exactly a big deal, as it is exactly the same effect as would result from requesting an input from any unconnected port. Still, it can be of some use in saving memory space in exactly the same way as the experienced programmer uses an

# **BIG HELP FOR SMALL BUCKS**.

Used to be, filling your bench with really good test equipment meant emptying your wallet. Because you had to pay a price for quality and versatility. A high price.

Not anymore. CSC's ingenious new Design Mate<sup>™</sup> line of test equipment combines performance high enough for most lab applications with the kind of versatility and economy everyone can afford. Thanks to a number of new design concepts and manufacturing techniques.

Proof? Check the specs and prices below, then visit your CSC dealer for a demonstration. Or write for our catalog and distributor list.

CONTINENTAL SPECIALTIES CORPORATION

| •       |       | • |

|---------|-------|---|

| EASY DO | ES IT |   |

44 Kendall Street, Box 1942 New Haven, CT 06509 • 203-624-3103 TWX: 710-465-1227 West Coast office: Box 7809, San Francisco, CA 94119 • 415-421-8872 TWX: 910-372-7992 Canada: Len Finkler Ltd., Ontario

© 1976, Continental Specialties Corporation \*Manufacturer's suggested list Prices and specifications subject to change without notice. Design Mate 1 Breadboard/ Power Supply. \$49.95\*

**Design Mate 2** Wide-Range Function Generator. **\$64.95**\*

Design Mate 3 Precision R/C Bridge. \$54.95\* XRA instruction instead of a LAI 000 instruction to clear the accumulator. This "load -1" instruction only occupies one byte of program space as compared to the two bytes required by an ordinary immediate instruction.

The IN7 instruction is more useful. The ability to dynamically interrogate the front panel switches during the execution of the program allows the operator to modify the program operation without the need for complex console communication routines. This capability was known as program option switches on the IBM 1401 and similar machines and was once widely used in commercial applications.

Suppose that one had a program which printed mailing labels for a computer newsletter. To save postage, it is desired to send a certain issue only to those who have indicated an interest in the specific topics covered. For example, some persons want to read only about hardware design, while others are interested in applications, compiler writing, etc. Multiple interests are allowed.

If up to eight areas of interest are coded as bits in an option byte included in the machine readable address list, then a program can create any desired subset of the list just by comparing to see if any bit in the option byte matches the corresponding bit in the program option switches. (The programming to do this is quite simple. Point the memory registers to the option byte in the file buffer, read the switches with IN7, and the option byte with the NDM instruction, and skip printing with a JTZ if the option does not match the switches.)

Another possible application would be to write an output subroutine such that it checks the program option switches to see if it should write to a video display, a hardcopy device, or both. This technique could save a lot of paper during program checkout, or when just demonstrating an application, and still allow permanent reports when required.

If you don't have a Scelbi, you can still implement program option switches yourself by putting a few switches in a minibox and hooking it up as a regular input device. But the interesting question is: What hidden capabilities does your system have? All you need is a little imagination and an inquiring mind. Look at your own system. Compare the users manual with the logical structure in the CPU chip manufacturer's catalogue. Look for logical inconsistencies and restrictions. Try some experiments with your equipment. Maybe you too can discover some new abilities for your system. Whatever your computer, get to know the implementation as well as possible. You may be able to find similar hidden instructions.

Architecture refers to overall system design – implementation refers to the specific technical methods.

Here is a product which will be of interest to many BYTE readers. This is an electronically controlled variable speed digital cassette deck which can be adapted for use by the home computer experimenter. It is made by Triple I, a division of the Economy Company, PO Box 25308, Oklahoma City OK 73125. Its price is in the \$100 range and it should prove to be an excellent medium for totally automated data storage in personal computing systems.

EDITOR PROGRAM Shipping Strange

FOR BEGINNERS

BOOS

MONITOR ROUTINES

"8008" Monitor Routines Describes "Monitor Control" package to control operation from external "keyboard". Routines to examine and modify memory locations, CPU registers, set "breakpoints", "debug-ging" programs, control bulk storage I/O devices, and more. Includes subroutine explanations, flow charts, assembled highly commented program listing. Order today!

1195

listing. Order today!

ppd.

AN 8008

1495

Describes variations that can reside in 2K of memory. How to increase buffer size. How to manipulate "text" for "source listings" and other text preparations, routines discussions, flow charts, assembled listings, more. Order now!

ppd.

"8008" Editor Program

### "8008" SOFTWARE MANUALS

ppd. **Assembler Programs** For The "8008"

1795

ABREMOLER PROGRAMS

'en o'e'

For The "8008" Minimum length assembler program for 2K memory, plus sophisticated version for additional memory or more power. Includes fundamentals of operation, how to format "source listing", step-by-step analysis/presen-tation of subroutines, flow charts, listings of programs and lots more. Order yours today!

### SAVE \$5.35! BUY ALL 3 FOR ONLY \$39.50!

### "8080" SOFTWARE MANUALS

Three new basic, complete "MUST" manualsi "6080" Assembler Program operates easily in 4K bytes of RAM (including symbol table). Unique feature: How to accept mnemonics related to "8008" based machines on "8080", Includes all major routines, pertinent flow charts, highly com-

mented assembled listing and more. \$17.95, "8080" Editor Program identical to "8008" Editor, with machine codes for "8080", \$14.95. "8080" Monitor Floutines same functions as "8008" specifically developed to utilize expanded capabilities of "8080". \$11.95.

SAVE \$5.35! BUY ALL 3 FOR ONLY \$39.50!

### MACHINE LANGUAGE PROGRAMMING FOR THE **"8008"**

(and similar microcomputers)

Here's the detailed, basic manual you need to develop today's machine language programs. 170 pages. Illustrated. Easy-to-read, understand. Most techniques applicable to other micro-computers, including "8080". Floating-point arithmetic package is worth the price alonel Order today!

- · Detailed presentation of "8008" codes · Flow Charts

- Mapping Floating-point Package Debugging

- · Basic programs: loops, counters, masks

- ٠

- Organizing Tables Editing/Assembling Math operations I/O, Real Time Programming

- Maximizing memories And lots more.

Pricing, specifications, availability subject to change without notice. Prices for U.S. and Canadian delivery at book mailing rate. Add \$2.50 for each publication if Priority Air Service (U.S.) desired. Overseas include \$5.00 for each publication for Airmail Service.

Telephone: 203/874-1573

# Biorhythm for Computers

According to the biorhythm hypothesis, there is a reason for those doldrum days when even your computer refuses to communicate with you.

[NOTE: The ideas presented in this article are a hypothesis about human mental states and are not necessarily a valid predictive theory. One danger of computer programming is the assumption that a logically correct program which executes without bombing out will necessarily produce meaningful results. Whatever the final conclusion with regard to the biorhythm hypothesis, the calculation makes an interesting example of a BASIC language application program. . . . CH]

Joy and Richard Fox 1364 Campbell St Orlando FL 32806

There is no doubt that all living things have biological rhythms. The study of three of these rhythms in humans has led to the development of a **pseudo** science, biorhythm, that, through the use of computers, is growing in popularity in the United States. This article describes a program, written in BASIC, which you can run in your own computer to plot biorhythm curves.

The purpose of the program is to use the biorhythm hypothesis to "predict" physical, emotional and intellectual patterns that indicate up, down and critical days for any period of time. These predictions are based on what purport to be scientific studies of human behavior. Biorhythm people claim to have learned through their studies that a physical cycle occurs every 23 days, an emotional cycle occurs every 28 days and an intellectual cycle occurs every 33 days. The plotting of these rhythms is printed out as a two-dimensional graph on a Teletype or similar output device, showing the three cycles as a function of time.

The biorhythm hypothesis is nothing new. It was first proposed in the late nineteenth century by a Viennese psychologist and a German physician, each working separately. In the 1920s, an Austrian teacher added the 33 day intellectual cycle after studying the performance of high school and college students.

According to the biorhythm hypothesis, there is a reason for those doldrum days when even your computer refuses to communicate with you. Each of the three cycles oscillates between ups and downs. When your cycles are up, you feel physically strong, emotionally high or intellectually brilliant. When your cycles are down, you feel physically weak, emotionally depressed or intellectually dull. But the days to really watch out for are the transition days when you are crossing from a low to a high or a high to a low. It is during these transition days that you are especially susceptible to accident and illness. A few times each year, two or even all three of your cycles will cross the transition simultaneously. According to biorhythm people, these critical days are best spent quietly.

The biorhythm 'hypothesis has gained acceptance in a growing number of industries. In Japan, 2,000 businesses use biorhythm calculations. One Japanese firm reports a 35% reduction in computer data errors by assigning workers to other tasks when they are going through critical days. Another Japanese firm using biorhythm predictions claims to have reduced its yearly vehicle accident loss by 45%. An American survey of 1,000 industrial accidents showed that 90% of them occurred on critical days.

Mike Bertalot, a supervisor for United Airlines, estimates that between 6,000 and 8,000 of United's 40,000 employees are using biorhythm predictions as a guide for safety awareness. United uses the printouts, which they distribute to interested employees, as "an excuse to warn employees about safety." The result has been that some departments have shown a 50% decrease in accidents. It is not clear whether this reduction is due to the extra warnings or to the predictive value of the hypothesis. Although the future of the biorhythm experiment at United is uncertain, the results are being sent to the United States Naval Laboratory, which is studying the hypothesis.

Biorhythms have also been used for profit. The September 15 1975 issue of *Newsweek* quotes Lester Cherubin, president of Time Pattern Research, Inc, as having sold 100,000 biorhythm printouts for \$10 to \$20 each in the past three years. Other companies sell plastic biorhythm calculating devices for anywhere between \$4 and \$20. Some shopping center vendors sell for a mere 50 cents a computer printout of your rhythms for one day.

The calculation of biorhythm curves is not easy to do with a pencil and paper. First, the subject's age in days must be calculated. This problem, of course, is complicated by all the peculiarities of the modern calendar. Then you must calculate how many complete 23 day cycles the subject has lived through and how many days he is into the next cycle. (The biorhythm hypothesis makes a simplifying assumption that all cycles originate at birth with zero relative phase.) The same must be done for the 28 and 33 day cycles. The fraction of each cycle is multiplied by two pi radians and the sine of that number is taken to obtain the points of the biorhythm curve for that day. The calculation must be rerun for each succeeding day, and the results plotted on graph paper, in order to obtain the biorhythm curves.

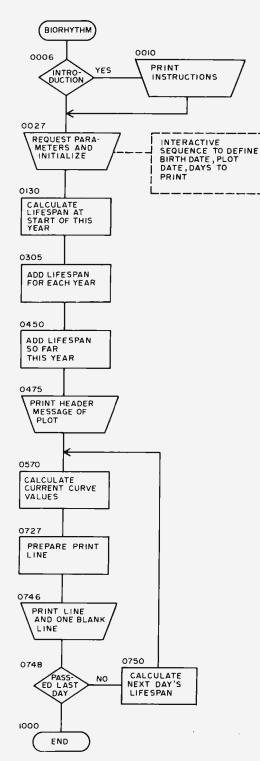

The program to calculate biorhythm curves is shown in the form of a flow chart in figure 1; figure 2 shows the complete listing of this program in BASIC. The operation of the program is as follows:

Line 0001 dimensions the strings N and S and the array T. N will be filled with the character set for the days of the month and S will be filled with the image of each line of the graph, as it is prepared for printing. T will be filled from the data statement at line 0080 with the number of days in each month of the year. The input statement at line 0008 and the if statement at line 0009 together allow the user to skip over the explanatory printout at the beginning of the program and go directly to the calculation which starts at line 0027.

Line 0040 defines the numeric values for the month, day and year that the subject was born. Line 0050 defines the month, day and year for the start of the printout. The year can be supplied as a two digit number ('76) or as a four digit number (1976), but the same format must be used for both the birth date and the printout target date. Line 0065 defines the number of days to be plotted.

D3 in the program is the variable which will contain the age of the subject in days. At line 0130, D3 is initialized to 0. The program will now calculate the number of days between the subject's birth date and the requested plotting date. The calculation is performed in several steps, and at the end

Watch out for evil omens on transition days.

While not intended to apply to machines, maybe biorhythms can be used to predict computer behavior. Enter the birth date of your computer and predict when your cybernetic monster plans its next bomb out!

of each step, the value calculated at that step is added to the total in D3.

Next, the program checks if the subject was born in January or February of a leap year. The test for a leap year, at line 0150, is made by dividing the birth year by four and checking for a remainder. Only leap years divide by four with a remainder of zero. If the subject was born in January or February of a leap year, one day is added to the running total, at line 0160. Otherwise, the running total is left at zero. Figure 1: Flow Chart of Biorhythm Calculator. This chart illustrates the general outline of the program found in figure 2. The numbers noted next to symbols in the flow chart refer to line numbers of the listing in figure 2.

0001 DIM NS(72), SS(72), T(12) NS-"0001020304050607080910111213141516171819202122232425262728293031" REM BIORHYTHM CREATED BY JOY AND RICHARD FOX PRINT "DO YOU WISH AN INTRODUCTION TO BIORHYTHM? TYPE 1 FOR YES," 0004 0006 0007 PRINT "OR 0 FOR NO " INPUT A IF A=0 THEN 27 PRINT TAB(25), "BIORHYTHM" 0000 0000 0010 0011 0012 0013 0015 0016 0017 0018 0020 0021 0022 0023 0024 0025 0026 0027 PRINT PRINT PRINT PRINT "THE PURPOSE OF BIORHYTHM IS TO PREDICT A PHYSICAL." PRINT "EMOTIONAL AND INTELLECTUAL PATTERN THAT INDICATES YOUR" PRINT "UP AND DOWN DAYS FOR ANY PERIOD OF TIME BIORHYTHM CAN" PRINT "SHOW WHICH DAYS WERE GOOD OR BAD FOR YOU BEGINNING WITH" PRINT "SHOW WHICH DAYS WERE GOOD OR BAD FOR YOU BEGINNING WITH" PRINT "OUR BIRTH. IT CAN ALSO SHOW YOU WHICH FUTURE" PRINT "SHOW WHICH DAYS WERE GOOD OR BAD FOR YOU" PRINT "THESE PREDICTIONS ARE BASED ON SCIENTFIC" PRINT "THESE PREDICTIONS ARE BASED ON SCIENTFIC" PRINT "THROUGH THESE STUDIES THAT A PHYSICAL CYCLE OCCURS EVERY" PRINT "THROUGH THESE STUDIES THAT A PHYSICAL CYCLE OCCURS EVERY" PRINT "INTELLECTUAL CYCLE OCCURS EVERY 23 DAYS." PRINT PRINT PRINT PRINT "PLEASE TYPE YOUR BIRTH DATE USING THE FOLLOWING FORMAT " PRINT "MM.DD.YY EXAMPLE JANUARY 17, 1942 - 01,17,42" 0028 INPUT M, D, Y PRINT "AT WHAT DATE ARE YOU INTERESTED IN BEGINNING BIORHYTHM" 0045 0050 INPUT M1, D1 PRINT "HOW MANY DAYS DO YOU WISH TO HAVE PLOTTED?" 0060 0065 INPUT D2 INPUT D2 DATA 31, 28, 31, 30, 31, 30, 31, 31, 30, 31, 30, 31 REM M-MONTH, D-DAY, Y-YEAR REM D3=TOTAL NUMBER OF DAYS ELAPSED D3=0 IF M>-2 THEN 200 IF (M>-2 THEN 200 D3=1 0110 0120 0130 0140 0150 0160 D3=1 FOR I=1 TO 12 0200 0210 READ T(I) REM T=DAYS IN EACH MONTH 0220 0230 0240 0250 NEXT I D3=T(M)-D+D3 FOR I=M+1 TO 12 D3=T(I)+D3 NEXT I 0260 0270 0280 REM Y3=YEAR COUNTER FROM BIRTH TO DISPLAY

HEM Y3-YEAR COUNTER FROM B.

Y3=Y

Y3=Y

Y3=Y1 THEN 400

IF Y3-=Y1 THEN 400

IF X3-=Y1 THEN 400

JS=D3-366

GOTO 299

IF M1-=2 THEN 450

IF INT(Y14)-(Y1 4)- 0 THEN 450

JG-B3-16

GOT1 TO M1.1

D3+T11)-D3

NEXT I

D3-103

PRINT "PHYSICAL CYCLE P"

0290 0299 0305 0310 0316 0316 0320 PRINT "PHYSICAL CYCLE P" PRINT "EMOTIONAL CYCLE E" PRINT "INTELLECTUAL CYCLE I" PRINT PRINT PRINT PRINT "DATE", PRINT TAB(13), "DOWN"; PRINT TAB(35), "CRITICAL"; PRINT TAB(63), "UP" PRINT "..... PRINT "......" PRINT "....." EET M4-M1 CET 04-D1 LET Y4-Y1 REM M4 D4.Y4 DATE PRINTED OUT IN PLOTTING CHART COTO COTO HEM M4\_04,Y4 — DATE PRINTED OUT IN PLOTTING ( GOTO 580 REM F-FRACTION INTO CYCLE F\*(03/23)INT(03/23) REM X-THE ARGUMENT FOR THE SINE FUNCTION X-F\*2\*3 1416 REM P-THE PHYSICAL POSITION ON THE GRAPH 0580 0600 0610 0640 0650 P={(SIN(X)+1)\*24}+15 REM E=EMOTIONAL POSITION ON THE GRAPH 0655 0660 0670 F=(D3/28)-INT(D3/28) X F\*2\*3.1416 X F <sup>2</sup>2 3.1416 E-(ISIN(X): 11) <sup>2</sup>4) <sup>1</sup>15 F <sup>2</sup>(D3/33) <sup>1</sup>NTID3/33) X F <sup>2</sup>2 3.1416 REM I-INTELLECTUAL POSITION ON THE GRAPH I-(ISIN(X)+11) <sup>2</sup>41+15 FOR X - 1 TO 32 SS(2<sup>2</sup>X 1.2<sup>2</sup>X) <sup>21</sup> <sup>21</sup> 0680 0690 0700 0710 0720 0727 0728 0729 0731 0732 0733 0734 0735 0736 0741 0742 0743 0744 0745 0746 0746 0747 0748 NEXT X S\$(39,39)-"" S\$(P,P)="P" S\$(E,E)="P" S\$(E,E)="E" S\$(1,1)-"1" S\$(3,3)="/" SS(3,3)="/" SS(6,5)=NS(M4\*2+1,M4\*2+2) SS(1,2)=NS(M4\*2+1,D4\*2+2) SS(1,2)=NS(D4\*2+1,D4\*2+2) IF Y4>99 THEN 950 SS(7,2)=NS((INT(Y4/10)\*2+2),(INT(Y4,10)\*2+2)) SS(7,2)=NS((Y4-INT(Y4/10)\*10)\*2+2,IY4 INT(Y4+10)\*10)\*2+2) PRINT SS(1,63) PRINT PRINT Sector PRINT IF D2-1 THEN 1000 IF D2-1 THEN 1000 D2-D2-1 D3-D3+1 D4-D4+1 IF M4<>2 THEN 820 IF D4<<29 THEN 820 IF D4<<72 THEN 820 IF INT(Y4)4| Y4/4| \0 THEN 820 GOTO 570 IF D4<=7 (M4) THEN 570 M4-M4+1 D4-1 0748 0750 0800 0810 0815 0815 0816 0817 0818 0820 0830 0835 M4 - M4 + 1 D4 - 1 IF M4.-12 THEN 870 GOTO 570 M4 - 1 Y4 - Y4 + 1 0840 0850 0870 0880 0900 GOTO 570 0950 4-Y4-(INT(Y4/100)\*100) 0951 GOTO 744 END

Figure 2: BASIC Program of the Biorhythm Calculator. This is the complete listing of a BASIC program to perform calculations and plot the results on a hard copy printer.

Lines 0200 through 0230 fill the array T with the values in data statement 0080 so that the array contains the number of days in each month of the year. Line 0240 calculates the number of days from the subject's birth date to the end of his first calendar month, and adds that number to the running total in D3. Lines 0250 through 0270 calculate the number of days in each month during the remainder of the subject's birth year, and add that number to the running total.

The birth year, Y, is transferred to the year counter Y3, and the year counter is incremented at line 0299. If the year counter is greater than or equal to the year to be printed out, Y1, then the program jumps to line 0400. Otherwise, the program adds 365 or 366 to the running total for each year between birth and the target year. Each time that is done, the year counter is incremented. When it matches the printout target year, the program jumps to line 0400.

Next the program calculates the number of days between the start of the display year and the display day. If the display month is March or later, then the program checks if the display year is a leap year. If it is, one day is added to the running total at line 0410. Lines 0450 through 0460 add the number of days in each month between the start of the display year and the display month to the running total D3. Line 0470 adds the number of days into the display month to the running total. D3 now contains the age of the subject in days, as of the requested display date.

Lines 0475 through 0526 print the header of the graph. Lines 0530 through 0571 set up three new variables, M4, D4, and Y4, which will contain each consecutive date as it is printed out.

Now the program calculates the phase of each of the three biological cycles for the subject for the dates requested. The physical cycle has a period of 23 days. If you divide the age of the subject in days by 23, the remainder is a number between 0 and 22.9. That remainder is proportional to the phase of the subject's physical cycle at the requested date. The remainder is stored in variable F at statement 0580. F is then multiplied by two pi radians and the answer is stored in X. X is therefore a number between zero and two pi and is proportional to the phase of the subject's physical cycle. Line 0650 takes the sine of X. The result is a value between +1 and -1. This number is then normalized to a value between 15 and 63 and is stored in P. The values 15 and 63 represent the beginning and ending column numbers of the graph on the Teletype.

Extreme down days will plot in column 15. Extreme up days will plot in column 63. Critical days will plot in column 39, and other days will plot in between these points.

The same calculation is then repeated at lines 0660 through 0680, with a period of 28 days, for the emotional cycle; and at lines 0690 through 0720, with a period of 33 days, for the intellectual cycle. Lines 0727 through 0729 loop to fill up the string S with blank characters, to wipe out old data still in the string. Line 0731 places a dot character in element 39 of the string, so that the zero crossing will be clearly marked by a string of dots down the 39th column of the page. Line 0732 stores the character "P" into the column calculated by the equation for the physical cycle. Lines 0733 and 0734 do the same for the characters "E" and "I". Next the program places slashes in elements three and six of the string S, so that they will print out as slashes in the date at the left of the graph.

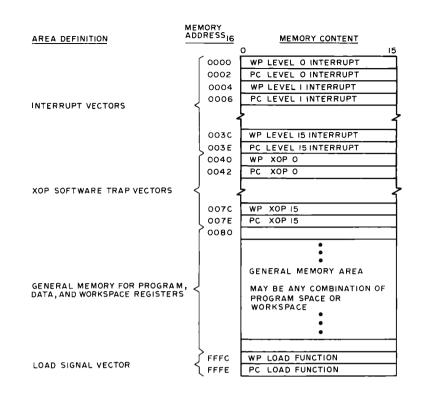

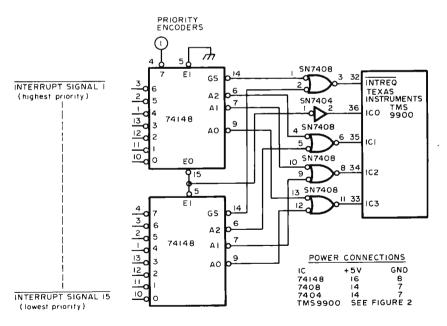

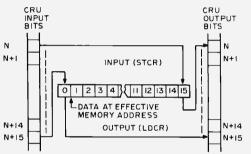

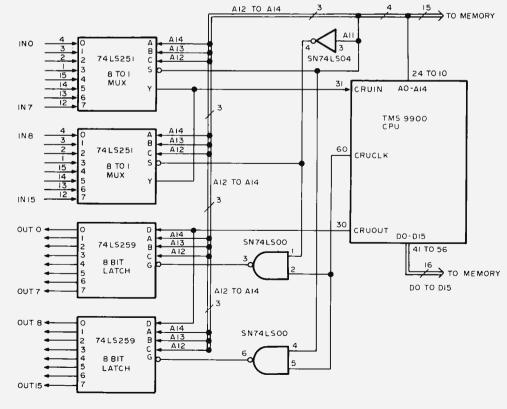

The month is placed in array elements one and two and the day is placed in elements four and five. If the operator typed the year as a four digit number, the program truncates the most significant two digits. Line 0744 places the ten's digit of the year into element seven of the string and line 0745 puts the unit's digit of the year into element eight.